[ad_1]

“Things that move around – cars, robots and drones – will increasingly have functional safety requirements,” Imagination v-p business development Steve Evans told Electronics Weekly

The firm has aimed the intellectual property, dubbed I6500-F, at ASIL D decomposed to B (ASIL B(D)) – meaning that it meets ASIL B un-aided, and is capable of meeting ASIL D if customer does the right thing around it.

It has been developed as a ‘safety element out of context’ (SEooC) product, so it is a standard product that can be re-used across a range of designs.

“The I6500-F design safety lifecycle aligns closely with the component vendor safety lifecycle, based on ISO 26262, 2011 1st Edition standard but already considering best practices for IP from Part 11 to be present in the 2nd Edition of ISO 26262 and already available in the published DIS version,” said the firm.

“The I6500-F design safety lifecycle aligns closely with the component vendor safety lifecycle, based on ISO 26262, 2011 1st Edition standard but already considering best practices for IP from Part 11 to be present in the 2nd Edition of ISO 26262 and already available in the published DIS version,” said the firm.

Spanish firm ResilTech was bought in to cast an independent eye over the I6500 to see what needed to be done for functional safety applications.

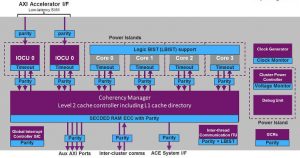

Following the survey, the design received, for example: built-in self-test logic which looks for hard faults, like static damage, in the chip during run-time; error correction (ECC) which protects against soft errors; and time-outs to detect if a requested resource does not respond in a timely manner (see diagram).

“It has to meet a single-point-failure metric of 90% and latent fault metric of >60%,” said Evans.

Compulsory documentation is part of functional safety, and a safety work product package will be available for the I6500-F, including safety cases such as an independent FMEDA safety analysis report by ResilTech to support customers in meeting ISO 26262. Imagination will also provide a ‘safety consultancy support’ package to help customers with integration and preparation of safety analysis at the SoC level for target ISO 26262 compliance.

MIPS I6500-F, and the earlier I6500, are 64bit, multi-threaded, multi-core, multi-cluster CPUs that can be scaled across a wide range of performance – up to 384 cores.

Both can coherently implement various configurations of CPU cores within a cluster (dubbed ‘heterogeneous inside’) and a variety of configurations of CPU clusters and GPU or accelerator clusters on a chip (dubbed ‘heterogeneous outside’).

Features including simultaneous multi-threading and hardware virtualisation are available with ‘zero context switching’ for applications requiring real-time response, and it is can have the firm’s ‘OmniShield’ security-by-separation functions.

Artificial intelligence appications are high on MIP’s agenda.

“Customers can use the extended performance capability of the I6500-F to efficiently integrate increased intelligence – including artificial intelligence techniques such as convolutional neural networks and deep neural networks in their safety-critical devices,” said the firm.

Mobileye was a lead customer. Its EyeQ4 SoC for automated driver assistance already uses MIPS’ interAptiv and M5150 CPUs with software self-core test, designed for ASIL B. Now its next-generation EyeQ5 SoC for autonomous vehicles, to be manufactured on a 7nm finFET process, is based on the I6500-F CPU.

[ad_2]

Source link