[ad_1]

- vehicle corner radars, which have to be physically small

- vehicle urban front radars, which need a wide field of view

- vehicle narrow-beam highway radars?

Texas Instruments said ‘yes’ in an ISSCC paper devoted to a single‑chip 76GHz-81GHz frequency-modulated continuous wave (FMCW) radar transceiver in 45nm CMOS, which includes three transmitters, and four receivers with integrated ADCs.

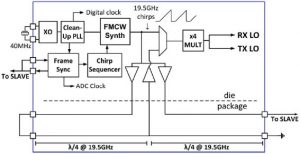

To support system-level functional safety, the design also features autonomous fault monitoring of the RF chain. The fast-chirp FMCW signal is generated in a closed-loop 19GHz‑20.25GHz fractional-N frequency synthesiser, fed from a high frequency reference clock via an integer-N clean-up PLL to suppress its quantisation noise. The synthesizer output is multiplied by four and then distributed to the Tx and Rx channels.

For MIMO radar use, each transmitter supports independent binary phase modulation and on/off keying, and each transmitter has a 6° step‑phase shifter for long-range beam forming.

A four-way power-combined PA delivers 12dBm(typ) to a waveguide on the PCB.

The FMCW receive chain uses a complex (I/Q) baseband to reject LNA image-band noise, as well as offering crossing interferers detection using the image band energy/time information, and digital compensation of delay errors between receive channels – the latter important to match delays from different antennas, particularly in multi-chip installations with a lot of antennas.

Among the circuit blocks discussed was multiple-chip synchronisation for larger antenna arrays where the local oscillator of one chip can be distributed to up to three others to synchronise all four – maintaining oscillator phase noise coherence across all Tx/Rx pairs, and to reduce angle estimation errors by minimising delay between local oscillator and ADC sampling. Synchronisation is at ~19GHz, halving losses compared with sync at 76GHz.

To ease routing, each chip has a clock input/output pair on each side of the package, backed by two output buffers, but only one input buffer.

One or both of the master outputs are used, depending on routing needs, to deliver equally timed clocks, including to the master’s own clock input.

The single input buffer is allowed through packaging cunning (diagram above), where a λ/4 transmission line in the package allows a short-circuit at the package ball to appear as an open circuit at the T-junction inside the chip, minimising loss and reflection for the employed path.

To provide ~1ns common chirp envelope timing and ADC synchronisation, at the start of every frame the master’s frame sync sends a single digital edge to all chips symmetrically, synchronised to the clean-up PLL.

The clock system demonstrates -94dBc/Hz phase noise (1MHz offset 76GHz‑77GHz) and <−91dBc/Hz up to 81GHz with better than 0.1% non‑linearity for a 4GHz ramp at 100MHz/μs.

An on-board ARM MCU autonomously monitors key RF performance parameters – a directional coupler power detector at the TX output detects faults in the PA or the package, while Rx gain, noise figure and phase imbalance are detected using a loopback signal.

The die is implemented in a nine metal layer 45nm bulk CMOS process, with its RF transceivers occupying 22mm2, flip-chip assembled into a standard automotive-quality BGA package.

The radar consumes 3.5W from 1V/1.2V/1.8V supplies. Intel and Uhnder worked alongside TI.

ISSCC paper 9.1

A Multimode 76-to-81GHz automotive radar transceiver with autonomous monitoring

ISSCC 2018

The IEEE’s annual International Solid-State Circuits Conference is the place where the world’s companies and universities gather to show off their chip-based circuit developments, and where attending engineers get a first glimpse of the state-of-the‑art in digital, analogue, power and RF design techniques.

[ad_2]

Source link