[ad_1]

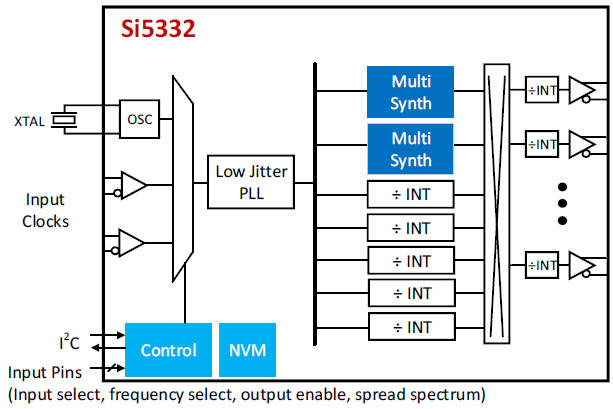

Called Si5332, 230fs(rms) general jitter performance is claimed, with specific examples of: 245fs for clocking system PLLs, 196fs for SerDes PLLs, 220fs for PCIe Gen4 (16Gtransfer/s)and 366fs for FPGAs.

The chip comes in three versions, with six, eight or 12 outputs.

All versions work from a single crystal and have two of the firm’s ‘MultiSynth’ fractional-n synthesisers and five integer synthesisers.

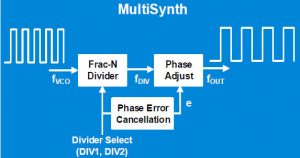

MultiSynth (see diagram below) reduces the phase-noise inevitable with digital fractional-n synthesys with a feed-forward phase error correction technique.

An integrated linear regulator also contributes to noise reduction.

Built on 0.13μm CMOS, consuming around 850mW depending on application.

Each output can be configured as LVPECL, LVDS, HCSL, or LVCMOS and supports 1.8-3.3 V.

On-board is non-volatile memory that boots the chip into operation in ~5ms, or is can be configured over a bus.

Applications are expected in data centre switches, servers, storage, networking, small cells, broadband, broadcast video, multi-function printers and industrial applications.

“Complex devices such as Ethernet switches, high-speed switch fabrics, network processors, server SoCs and FPGAs combine data path processing, CPU functions and multiple SerDes into a single IC,” said Silicon Labs. “As a result, these devices require a diverse combination of reference timing. 10/25/100G SerDes have stringent jitter requirements, often requiring clocks with <300 fs rms maximum jitter performance.”

[ad_2]

Source link