[ad_1]

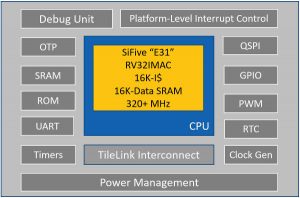

Called the Freedom E301 or FE310, alongside the RISC-V core are a whole bunch of peripherals (see diagram).

The core runs at 320MHz, so this is a powerful beas, and it supports the following RISC-V specifications:

- RV32I base integer instruction Set v2.0

- ‘M’ standard extension for integer multiplication and division v2.0

- ‘A’ standard extension for atomic instructions v2.0

- ‘C’ standard extension for compressed instructions v1.9

- RISC-V privileged ISA specification v1.9.1

- RISC-V external debug support v0.11

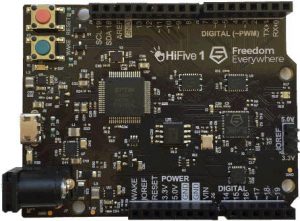

The development board is called HiFive, and includes the FE310 running at full speed.

The development board is called HiFive, and includes the FE310 running at full speed.

Combined, the chip and board specs are:

- 1.61 DMIPs/MHz

- 2.73 Coremark/MHz

- 16kbyte instruction cache

- 16kbyte data scratchpad

- 3.3 and 1.8V operation

- 5V over USB or 7-12V jack board power

- 3.3 or 5V I/O

- 19 digital I/O pins

- 9 PWM pins

- 19 external interrupt pins

- 1 external wake pin

- 128 Mbit off-chip flash

- Micro USN host interface for programming, debug and comms

- 68 x 51mm 22g

The firm, which appears to have been started by the fellows who started work on the RISC-V instruction set at Berkley, is also working on intellectual property to implement 32 (‘E3’) and 64bit (‘U5’ 1.6GHz at 28nm) versions of RISC-V cores on SoCs.

As far as I can make out, the RISC-V instruction set (supported by the RISC-V Foundation, which includes Google and IBM) is available for anyone to use for free under an open source license, while, I am guessing (do please correct me if necessary), the cores will be licensable.

I also guess that the silicon is there to build confidence in the architecture – which could be a free competitor to MIPS and the mighty ARM for anyone who wants to do the implementation leg-work.

[ad_2]

Source link