[ad_1]

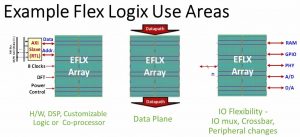

“Data centers require reconfigurable hardware protocols for networking, storage and security, and therefore switches, NICs and other networking chips need very high-performance reprogrammability,” says Geoff Tate, CEO and co-founder of Flex Logix, “likewise, deep learning accelerators integrated on-chip for high bandwidth and future base station chips also need high-speed reprogrammability. The high-density, high-performance EFLX 2.5K embedded FPGA enables this ability in chips cost effectively and at high performance.”

The EFLX-2.5K embedded FPGA core in TSMC 16FF+ and 16FFC has been optimized for high performance at worst-case PVT conditions. The EFLX-2.5K can be “arrayed” to build any size embedded array required, from 1×1 (2.5K LUTs) up to 7×7 (122.5K LUTs).

Flex Logix offers logic and DSP versions and both are interchangeable in an array, with the logic version being all programmable logic. The DSP version substitutes some LUTs for 40 Multiplier-Accumulators, each with pre-adder, 22×22 bit multiplier and 48-bit accumulator. Even the smallest EFLX-2.5K array has >1000 CMOS I/O allowing connections to multiple wide, fast on-chip buses.

The 16nm version of EFLX-2.5K is based on a 2nd generation architecture with numerous, patent-pending improvements that will be incorporated into all future EFLX implementations:

· 6-input LUTs (that can also be dual 5-input LUTs) each with dual outputs and dual, optional flip flops. This enables more processing to be done in a single stage for higher logic density and higher performance.

· The proprietary interconnect has been further improved for even higher performance, especially for larger arrays.

· MACs are pipelined 10 in a row to provide local interconnect for FIR filters, etc with even higher performance than using the general interconnect.

· DFT enhancements for high fault coverage.

· A new test mode enables much faster test times.

· Readback circuitry enables configuration bits to be read back to check as frequently as desired for soft errors to improve reliability for high-rel applications.

· The core operates over all nominal voltages supported by TSMC 16FFC/FF+.

· The core requires only 6 routing layers of metal and is compatible with almost all metal stacks.

· An EFLX-2.5K IP core in TSMC 16FF+/FFC has an area of 1.0 mm2. Significant power/ground busing has been integrated to ensure reliable performance at high utilization, high switching and high frequency operation at worst case PVT conditions.

The design deliverables for each EFLX Core and EFLX Array includes GDS-II, LIB, LEF, Verilog model, CDL/SPICE netlist, Test Vectors, Validation report, detailed Datasheet, Integration Guidelines & the EFLX Compiler.

EFLX Compiler for TSMC 16FFC and 16FF+

The software for programming and checking timing performance will be available shortly for TSMC 16FFC EFLX-2.5K arrays; and on demand for TSMC 16FF+.

Flex Logix offers software evaluation licenses at no cost to enable customers to check RTL performance and area interactively for new architecture ideas.

The validation chip for these new IP cores will include a 7×7 array mixing 35 logic and 14 DSP cores, resulting in 114,240 LUTs and 560 MACs surrounded by 4,424 inputs and 4,424 outputs. The validation chip is in fabrication now and evaluation boards will be available under NDA to customers.

Flex Logix proves out all of its IP cores in silicon for each major process node to ensure low risk of integration, even though its IP is all digital and compatible with logic DRC rules and the IP is simulated under worst-case conditions.

These conditions include maximum frequency, high utilization and RTL with very high toggle rates to check for worst case static and dynamic IR drops.

Validation verifies in silicon that the recommended power grid architecture enables full-speed operation at full utilization with high toggle rates under worst-case conditions.

The company checks enough array combinations to be sure that the inter-core array-interconnect is functional on all sides, thus ensuring array reliability.

Flex Logix uses an on-chip PLL to test on-chip at frequencies of 1GHz+ and above to confirm all functional and performance operation over the full temperature and voltage range.

Each EFLX array interconnects with external I/O for test and with on-chip SRAM for high-speed pattern testing. A process, voltage and temperature monitor ensures precise control over testing at worst case conditions.

Power domains are dedicated to each EFLX array and separately for SRAM and I/O and PLL so voltage range can be measured precisely for each IP. Once validation is complete, a detailed validation report will be available under NDA to interested customers.

[ad_2]

Source link